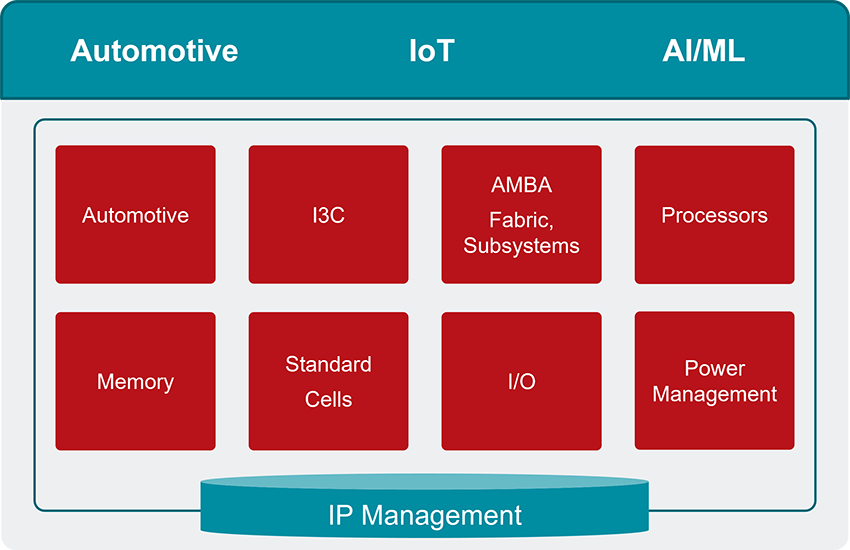

Silvaco IP products and solutions include embedded processors, wired interfaces, bus fabrics, peripheral controllers, and cores for automotive, consumer and IoT/sensor applications. Our catalog of IP meets the requirements for different consumer, mobile, and HPC applications including wired and high-speed interfaces, analog and mixed-signal blocks.

Automotive IP

Embedded Memory Compilers

I3C Solutions

Standard Cell Libraries

AMBA Cores and Subsystems

Interface IP

Embedded Processors

Power Management

Contact Silvaco if you need additional info on a specific IP or you do not see the IP product you require.

Learn How SilTerra Uses Cello and Viola for Standard Cells and I/O Library Optimization and Characterization

Learn About Silvaco’s AMBA AHB Subsystems and How to Customize, Secure, and Verify

Managing the Complexity of FinFET Standard Cell Layout with Cello

Designing with Silvaco’s Octal SPI Memory Controller with Advanced Memory Support for IoT Systems

Achieving Extreme Low Power IoT Designs with Silvaco’s 55LPx Foundation IP Solution